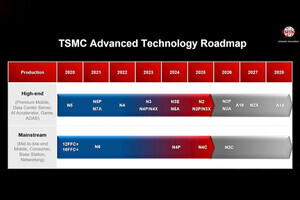

前回は、VLSIシンポジウム2025における回路設計分野の注目論文として、無線通信、トランスミッタ、データコンバータの紹介を行ったが、今回はイメージセンサ(ソニー、キヤノン)、ヘテロジニアスSoC(カリフォルニア大学)、クロック逓倍回路(アイルランド国立大学)、SRAM(TSMC)に関する論文を紹介する。

イメージセンサの注目論文

- A 25M points/s Back-Illuminated Stacked SPAD Direct Time-of-Flight Depth Sensor with Equivalent Time Sampling for Automotive LiDAR(25M 点/秒で測距可能な車載LiDAR向け裏面照射積層型SPAD直接ToF方式距離センサ) (論文番号:C27-2)

ソニーセミコンダクタソリューションズの研究グループは、ヒストグラム蓄積、信号処理、データ出力のパイプライン化とチップ内距離情報抽出処理による出力データ量の削減により、25M点/秒の測距を実現したことを報告する。

この実現により、自動運転レベル3以上に必要なLiDAR性能である視野角水平120°/垂直26°、角度分解能0.05°とフレームレート20fpsを両立した測距を実現したという。また、多相クロックを用いた等価時間サンプリング方式を活用することにより、データ量を増加させずに測距分解能を向上し、250mの距離にある25cmの物体検知や、300mまでの測距レンジにおいて最大17cmの測距誤差を実現したとしている。

- 2/3-inch 2.1Megapixel SPAD Image Sensor with 156dB Single-Shot Dynamic Range and LED Flicker Mitigation based on Weighted Photon Counting Technique(重み付けフォトンカウント技術による156dB単露光ダイナミックレンジとLEDフリッカー低減機能を備えた2/3インチ2.1MピクセルSPADイメージセンサ) (論文番号:C27-1)

キヤノンの研究グループは自動車用途向けのSPADイメージセンサを発表する。新たな重み付けフォトンカウント技術を提案し、LEDフリッカー低減機能とシームレスなグローバルシャッター機能を搭載しながら、156dBのダイナミックレンジを達成したという。さらに、ノイズレス読み出し動作により、0.1ルクス未満の低照度環境でも画像の撮影が可能となることを実証したとしている。

プロセッサ/SoCの注目論文

- MAVERIC: A 16nm 72 FPS, 10 mJ/frame Heterogeneous Robotics SoC with 4 Cores and 13 INT8/FP32 Accelerators(16nmプロセスによる4コア・13個のINT8/FP32アクセラレータを備えた72FPS,10mJ/frameロボティクス向けヘテロジニアスSoC) (論文番号:C10-5)

3次元再構成を用いるロボティクス向けアプリケーションでは認識タスクにおいて深さ推定(DE)や自己位置推定・同時マッピング(SLAM)のために高い計算性能が必要になる。

カリフォルニア大学バークレー校の研究者らは、4個のCPUコアと13個のINT8/FP32のアクセラレータユニットを有する、機械学習やロボティクス向けのヘテロジニアスSoC(MAVERIC)に関する研究成果を報告する予定である。MAVERICは最高1GHz動作にて8TOPS/Wのピークエネルギー効率を実現したほか、ループ閉じ込みに対応し、DEとSLAMのエンドツーエンド動作にて10mJ/frame、72FPSの性能を実証したという。

-

(上)MAVERICのアーキテクチャ概略。8個のINT8 MLアクセラレータ、 5個のFP32線形代数アクセラレータ、4個のRISC-V CPUと各サブブロックをつなぐ 3階層のNoCからなる。(b)チップ写真およびSLAM動作例を含む性能概略